Throughout the TEAChER project we aim to develop educational material for teaching topics related to the 2D and 3D reconfigurable architectures. More specifically, during these lessons we plan to address both architectural-oriented issues, topics related to CAD algorithms, as well as efficient ways for digital design with the usage of advanced programming languages. As there are different demands for training in this domain, the developed material will be appropriately tuned for the target audience, spanning from undergraduate studies up to PhD. For this purpose, we plan to prepare slides, presentation, books, CD/DVDs, as well as laboratory exercises for each of these topics. Apart from the conventional educational methods that will be taken into consideration during the preparation of this material, we aim to develop a virtual classroom, where students will have remote access both to theoretical, as well as laboratory infrastructure. Another outcome of this project is expected to be a number of workshops and summers schools, where Professors and key persons from related industry will give lectures.

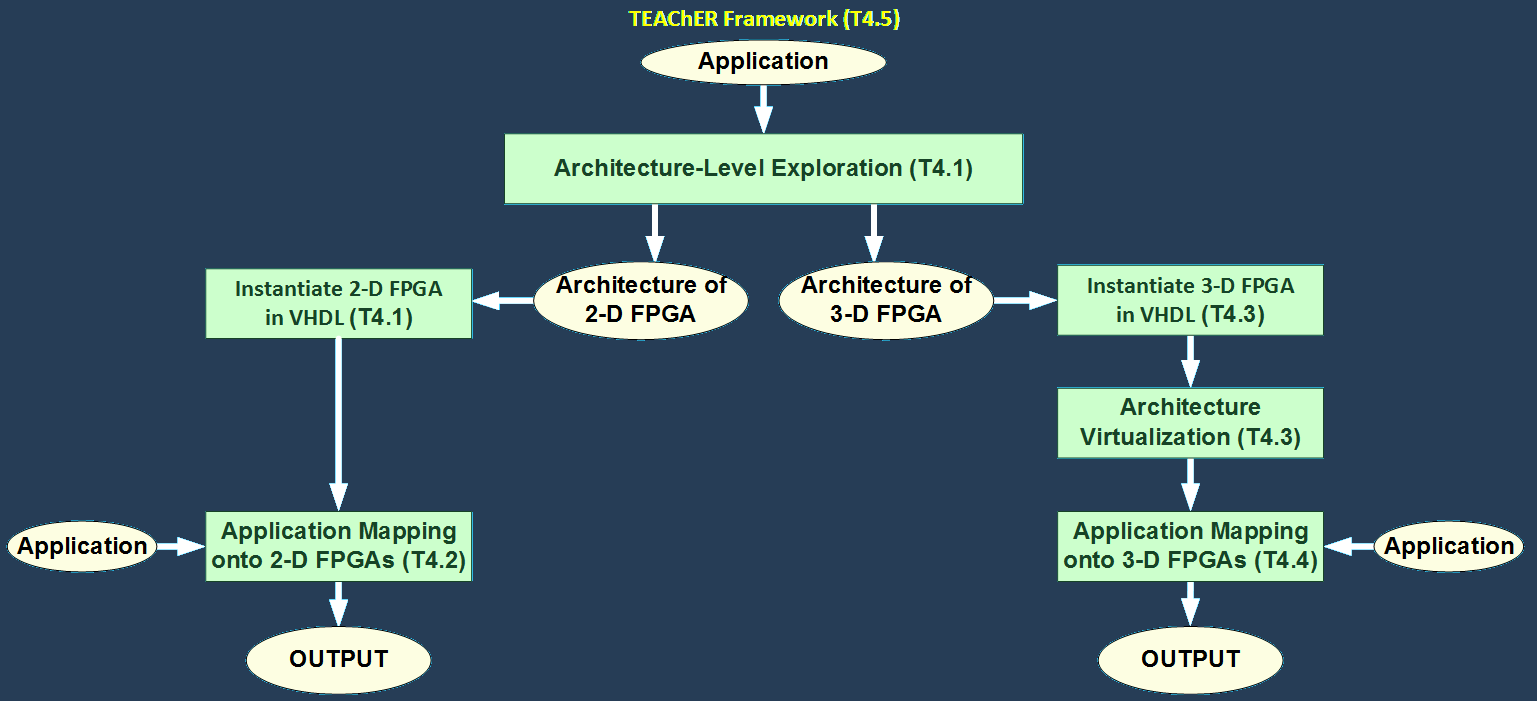

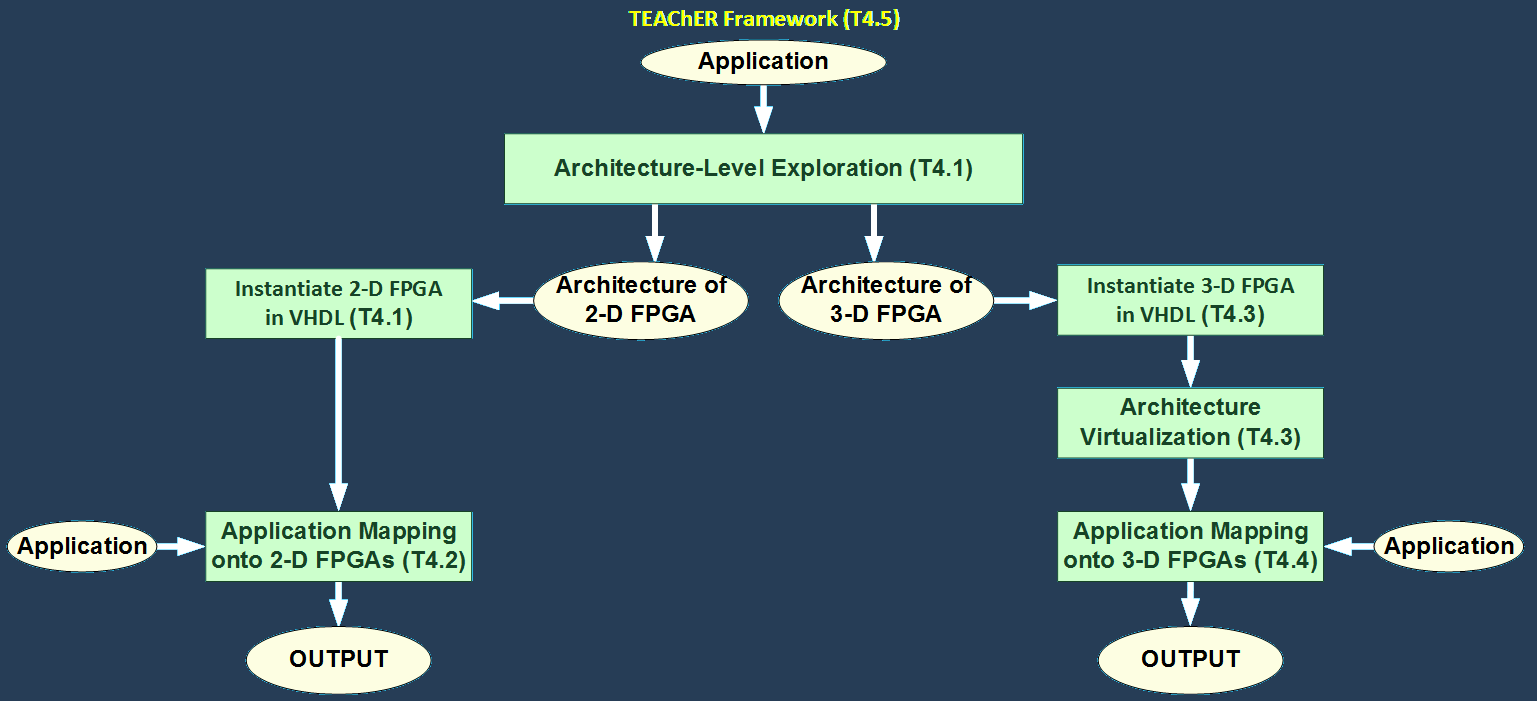

Starting from an application, initially we perform architecture-level exploration in order to determine the most suitable reconfigurable architecture for application implementation. During this analysis, a number of application's properties are identified. Among others, the memory requirements, the demands for supporting high-speed connectivity among distinct kernels, as well as the existence, or not, of complex arithmetic operations (e.g. floating-point operations) are identified.

The conclusions of this step provide an overview for the architectural organization of the target reconfigurable device. These parameters are appropriately handled in order to instantiate in VHDL (VHSIC Hardware Description Language) the architecture description of the FPGA. An initial form of this description regarding the 2-D FPGA instantiation was already available to the consortium, for previous collaboration between KIT and ICCS. However, for the scopes of the TEAChER project, this description should be appropriately modified in order to be used also for academic purposes.

In case we are studying the 2-D flow, then the VHDL description of Virtual FPGA (V-FPGA) is mapped onto an existing reconfigurable platform (e.g. provided by Altera or Xilinx), whereas the application mapping onto the VFPGA is performed with the extended version of 2-D MEANDER flow. Otherwise (3-D branch), the VHDL description of V-FPGA has to be appropriately modified in order to take into consideration inherent constraints posed by the third dimension (i.e. the existence of vertical connections that minimize the wirelength of long connections). Then, the V-FPGA is mapped onto an appropriate hardware platform (e.g. Virtex-7), which is aware about the 3-D integration, and application is implemented on top of V-FPGA (similar to the 2-D flavor of our methodology). Next, we describe in more detail the concept of V-FPGA.